이번에는 OpenSPARC T2에 대해서 알아볼 차례입니다.

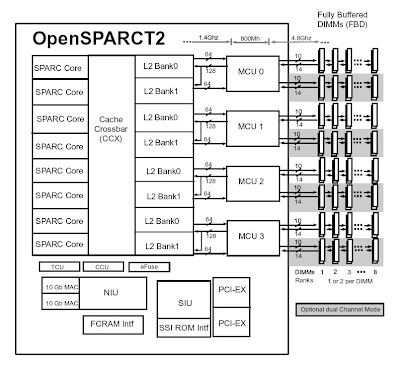

T2의 전체적인 구성은 T1과 큰 차이를 보이지는 않습니다. 8 개의 core가 crossbar bus로 8개의 bank로 나누어진 L2 Cache에 연결된 형태를 가지고 있습니다. L2 Cache는 총 4MB이고 16-way set associavity를 가진다고 합니다. L2 cache의 2개의 bank 마다 하나씩 memory controller가 연결되는데 Fully Buffered DIMM을 사용하도록 변경하였습니다.

T1과 다른 점은 우선 공유 FPU가 없어지고, FPU는 각 Core에 들어가게 됩니다. 그리고 10 Gbps Ethernet MAC 2 port와 PCI Express가 내장된 형태를 가지고 있습니다.

T1에 비해 Core의 내부가 상당히 많이 변경되었습니다. T2은 Integer Execution Unit 2개와, Float Point Unit 1개, Load Store Unit 1개로 구성됩니다. 기본적으로 8개의 thread를 동시에 exeuction 할 수 있습니다. 8개의 thread를 2개의 group으로 나누어 4개의 thread 중에 하나를 골라 instruction을 issue합니다. 2개의 group이므로 2개의 instruction을 issue할 수 있는 구조를 가지고 있습니다. Integer Execution Unit이 2 개이므로 2개의 integer instruction 조합, 1개의 integer instruction+1개의 floating point insturction, 1 개의 integer instruction + 1 개의 load/store, 1개의 load/store + 1개의 floating point instruction을 issue할 수 있습니다. floating point unit에서 integer multiply와 divide를 처리하므로 그것은 좀 예외적으로 처리됩니다.

Integer pipeline도 8 stage로 변경되어 Fetch/Cache/Pick/Decode/Execute(ALU)/Memory/Bypass/Writeback 순서로 되어 있습니다. Pick Stage가 T1에 있었던 Switch stage에 해당하고, Bypass stage는 Load/Store Unit의 latency가 더 크므로 그것을 보상하기 위해서 들어 있다고 합니다.

16KB 8-way set associative Instruction cache를 가지고 있고, 8KB 4-way set associative write through data cache를 가지고 있습니다. 모두 physically tagged virtually indexed cache로 보입니다. 64 entry fully associative IITLB와 128 entry fully associative DTLB를 따로 가지고 있고, T1과는 다르게 hardware tablewalk를 지원하는 것으로 보입니다.

UltraSPARC T2(코드명 Niagara II)로 발표되었을 당시(2007년)에 65 nm 공정을 사용하고 die size는 342mm^2로 알려졌습니다. 65 nm 공정으로 이동했고, L2 Cache의 크기가 큰 폭으로 증가하지 않았는데도 die area는 크게 줄지 않은 것으로 보아, FPU를 내장한 것이 큰 영향을 주었을 것으로 보입니다. 동작 주파수는 1.4 GHz입니다.

당연히 T1에 비해서 성능 향상이 이루어졌습니다. 우선 64 thread를 지원한다는 강점이 가장 크고, floating point 연산도 8개의 core에서 따로 수행할 수 있으므로 매우 빨라졌습니다. Clock frequency도 높아졌고, 다른 feature(L2 Cache의 size 등)도 좋아졌으므로 single thread performance도 어느 정도 향상되었다고 합니다. T2가 발표될 당시 SPEC 벤치마크에서 integer/floating point 연산 throughput에서 1등을 하였다고 하는데, 상당한 성능을 자랑했던 것으로 보입니다. 당연히 single thread의 performance는 다른 processor에 비해 느렸겠지만 throughput에서는 성능을 낼 수 있는 구조였으므로 가능했겠습니다.

Server에 집중할 거라면 굳이 FPU를 내장해서 Core 사이즈를 늘리지 말고, Core 갯수를 늘리거나 L2 Cache를 늘려서 integer 성능을 더 끌어올리는 방법이 어땠나 싶습니다. 어짜피 FLOPs로 판단하는 슈퍼컴퓨터 동네에서 IBM의 Power 시리즈를 누르기는 힘들었을 텐데 말이죠.

0 개의 댓글:

댓글 쓰기